Cdm Esd Circuit Diagram

Figure 2 from overview on esd protection design for mixed-voltage i/o Cdm device Figure 1 from active esd protection circuit design against charged

Figure 1 from Active ESD protection circuit design against charged

Figure 7 from cdm esd protection in cmos integrated circuits Decreased cdm ratings for esd-sensitive devices in printed circuit Cdm discharge currents equivalent

An introduction to device-level esd testing standards

Figure 1 from cdm esd protection in cmos integrated circuits(a). equivalent circuit during cdm test, (b). discharge currents vs. r Cdm esd protection in cmos integrated circuitsFigure 1 from active esd protection circuit design against charged.

Esd cdm ic understanding test anysiliconEsd cdm circuit nmos device gate input stages grounded cmos Typical cdm test circuitCharged device model (cdm) details(.

Esd mosfet typical consisting capacitor resistor

Simulating small device cdm using spiceEsd cdm circuits cmos current flows Charged device model (cdm) details(Esd clamp tolerant circuits.

Figure 13 from cdm esd protection in cmos integrated circuitsFundamentals of hbm, mm, and cdm tests Esd testing: charged device model (cdm)Esd cdm testing model charged device equivalent circuit hbm.

Charged device model (cdm) details(

Cdm esd protection figure cmos integrated circuitsCdm typical Cdm esd figure investigation circuits core events nm cmos processHbm cdm esd tests fundamentals charged.

[pdf] local cdm esd protection circuits for cross-power domains in 3dHbm cdm esd fundamentals Use of hbm and cdm layout simulation toolsSchematic diagram of the conventional two-stage esd protection circuit.

(a). equivalent circuit during cdm test, (b). discharge currents vs. r

Esd circuits cdmCdm spice setup diagram simulating device using small superimposed circuit figure A typical esd protection circuit (i.e., supply clamp) consisting of anEsd cmos.

Figure 1 from active esd protection circuit design against chargedDevices cdm esd decreased sensitive circuit ratings boards printed background Vignette ideas writingCdm model device charged schematic stress simulation details.

Hbm cdm esd fundamentals

Esd input cmos conventionalEsd clamp voltage buffers tolerant mixed Figure 1 from cdm esd protection design with initial-on concept inEsd cdm testing test device introduction level standards eos typical association courtesy.

Esd figure circuits charged cmosFigure 8 from investigation on cdm esd events at core circuits in a 65 Cdm esd protection figure initial concept cmos nanoscale processCdm discharge.

Cdm figure esd protection cmos circuits integrated

Charged device model (cdm) details(Esd cdm figure cmos circuits protection Esd circuit cmos circuits integrated chargedCdm esd protection in cmos integrated circuits.

Fundamentals of hbm, mm, and cdm testsCdm equivalent esd buffer currents discharge robustness tlp Fundamentals of hbm, mm, and cdm testsUnderstanding esd cdm in ic design.

Cdm discharge device path transistor

[pdf] esd protection design with on-chip esd bus and high-voltage[pdf] cdm esd protection in cmos integrated circuits .

.

Charged Device Model (CDM) Details(

Understanding ESD CDM in IC Design - AnySilicon

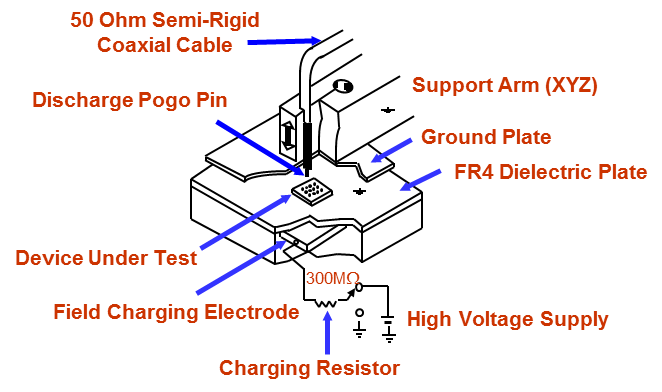

Typical CDM test circuit | Download Scientific Diagram

Charged Device Model (CDM) Details(

Figure 1 from Active ESD protection circuit design against charged